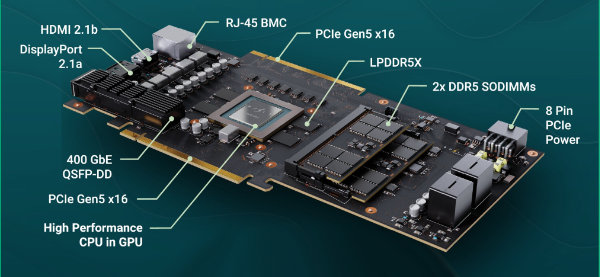

Suunnittelujen monimutkaistuminen ja viivanlevyksien kutistuminen on johtanut siihen, että suunnittelujen DRC-tarkistus eli suunnittelusääntöjen toteutumisen varmistaminen vie yhä enemmän aikaa. EDA-talo Cadence Design Systems helpottaa ongelmaa uudella suunnittelusääntöjen Pegasus-työkalullaan.

Suunnittelusääntöjen määrä on karkeasti ottaen kaksinkertaistunut jokaisen uuden prosessisukupolven myötä. Yhtiön mukaan tilanne oli kutakuinkin hallinnassa vielä 28 nanometrissä, mutta sen jälkeen DRC-tarkistus (Deisgn Rule Checking) on vienyt aikaa jopa neljä päivää (yli 100 tuntia) jokaista iteraatiokertaa kohti.

Pegasus mullistaa DRC-tarkistuksen massiivisella rinnakkaisuudella. Järjestelmä tukee tarkistuksen siirtämistä jopa 960 prosessorille. Aiemminkin näin on pienemmässä mittakaavassa voitu tehdä, mutta tällöin suorituskyky ei ole kasvanut prosessorien määrän kasvattamisella lineaarisesti. Pegasuksessa teho kasvaa käytännösäs lineaarisesti.

Käytännössä tämä tarkoittaa, että päiviä vievä DRC-tarkistus puristuu nyt tunteihin. Suunnittelun tarkistuksen voi jättää ajamaan palvelinfarmiinsa yön yli ja aamulla se on valmis analyysiä varten.

Pegasus kutistaa erityisesti tape out -tarkistukseen kuluvaa aikaa. Isoista suunnitteluista tarkistaa ensin suunnittelusäännöt lohkotasolla. Sen jälkeen siirrytään tarkistamaan DRC-aliosuuksia (jännite, valotuskuviointi, jne.), joissa jokaisessa aikaa säästyy merkittävästi. Käytännössä suunnittelua voidaan tarkistaa PCS-työkaluun verrattuna jopa 12-kertaisesti nopeammin.

Pegasus integroituu suoraan Cadencen Virtuoso- ja Innovus-alustoihin. Laskentaa voidaan skaalata myös kaupallisille pilvipalveluille tai yrityksen omaan palvelinhuoneeseen.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.