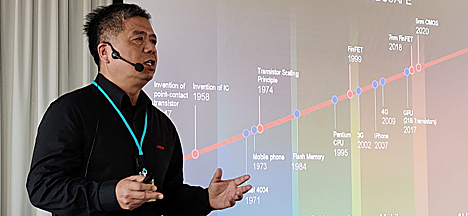

Kaikkein edistyneimmät mikropiirit valmistetaan tällä hetkellä seitsemän nanometrin prosessissa EUV-tekniikalla. Sopimusvalmistaja TSMC:n markkinoinnista Euroopassa vastaavan John Chinin mukaan seuraavaksi on vuorossa 5 nanometriä. – Teknisesti voimme nähdä, että kolme nanometriä on täysin mahdollinen, Chin sanoi eilen Mentor Forum -tapahtumassa Helsingissä.

Kaikkein edistyneimmät mikropiirit valmistetaan tällä hetkellä seitsemän nanometrin prosessissa EUV-tekniikalla. Sopimusvalmistaja TSMC:n markkinoinnista Euroopassa vastaavan John Chinin mukaan seuraavaksi on vuorossa 5 nanometriä. – Teknisesti voimme nähdä, että kolme nanometriä on täysin mahdollinen, Chin sanoi eilen Mentor Forum -tapahtumassa Helsingissä.

Chinin mukaan CMOS-logiikka kehittyy myös kolmen nanometrin jälkeen. – Puhutaan noin nanometrin viivanleveydestä, mutta sen pidemmälle tutkimuspuolemmekaan ei tiedä, hän kertoi.

Käytännössä puolijohdevalmistuksen tulevaisuus osataan kertoa siis noin viisi vuotta eteenpäin. Tällä hetkellä TSMC:llä on työn alla N6-prosessi, joka on GDS-yhteensopiva nyt linjalla olevan N7-prosessin kanssa. Periaatteessa suunnittelut siis voidaan viedä kuuteen nanometriin, jolla logiikan tiheys paranee 18 prosenttia.

- N6-prosessissa olemme aloittamassa riskituotantoa ensi vuoden ensimmäisellä neljänneksellä. Viiden nanometrin N5-prosessissa riskituotanto on alkanut jo maaliskuussa ja kaupallisesti prosessi tuodaan tarjolle ensi vuonna, Chin paljasti. Testipiirinä N5-kehityksessä käytetään nyt 112 gigabitin serdes-piiriä.

Chin muistuttaa, että TSMC on valmistusyritys. – Periaatteessa me vain kasvatamme ja leikkaamme, hän luonnehti. Luonnehdinta on tietysti hauska, koska kyse on yhdestä maailman vaativimmasta tuotannosta.

Uusimmat prosessit tulevat aina logiikkapiireihin, yleensä vielä vuosia ennen muita piirejä. Kun vaikkapa kännykkäpiirejä valmistetaan nyt 7 nanometrin viivanleveydellä, RF-piireissä sitä vasta suunnitellaan. – Ensimmäiset 7 nanometrin wifi-piirit voivat tulla markkinoille ehkä 2021, Chin arveli.

TSMC:n tekninen kehitys on ollut huikeaa. Esimerkiksi N7-prosessi on ollut massatuotannossa huhtikuussa 2018 lähtien, ja asiakkaille on toimitettu jo yli miljoona kiekkoa. – Vuodessa virheiden määrä kiekolla (defect density) on kutistunut pienemmäksi kuin N20- tai N16-prosesseissa. Mikään valmistusprosessi ei ole tullut valmiimmaksi N7:ää nopeammin, Chin kehuu.

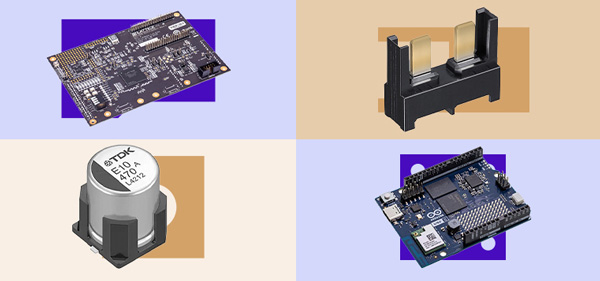

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.