Pitkään prosessoreissa yritettiin integroida mahdollisimman palon suoritinytimiä samalle sirulle. Tämä ei välttämättä ole kaikkein tehokkain ratkaisu. CEA-Leti -tutkimuslaitos esitteli piiritekniikan ISSCC-konferenssissa ratkaisun, jossa 96 ydintä liitetään toisiinsa kuuden pikkupiirin avulla.

Pitkään prosessoreissa yritettiin integroida mahdollisimman palon suoritinytimiä samalle sirulle. Tämä ei välttämättä ole kaikkein tehokkain ratkaisu. CEA-Leti -tutkimuslaitos esitteli piiritekniikan ISSCC-konferenssissa ratkaisun, jossa 96 ydintä liitetään toisiinsa kuuden pikkupiirin avulla.

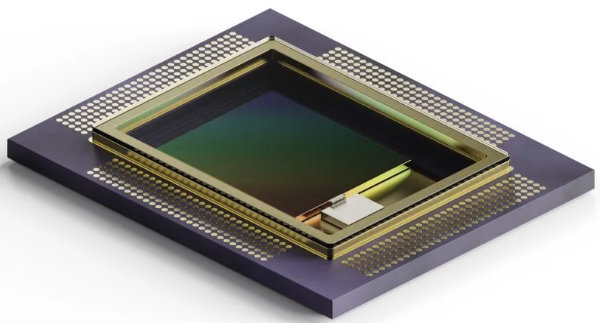

Näitä pikkupiirejä kutsutaan nimellä chiplets. CEA-Letin piirillä kuusi chiplettiä istutetaan vierekkäin piipohjaiseen välitys- eli interposer-kerrokseen. Tämän ansiosta ytimet kommunikoivat toistensa kanssa erittäin nopeasti.

Tutkijoiden mukaan piirin latenssi kirjataan 0,6 nanosekunniksi millimetriä kohti. Yhdellä neliömillillä data liikkuu pikkupiirien välillä 3 terabitin sekuntinopeudella. Nämä ovat sellaisia lukemia, joihin ei perinteisissä SoC-rakenteissa päästä.

Myös arkkitehtuurin tehonkulutus on erittäin pieni. Tehoa kuluu 156 milliwattia neliömilli kohti. Osin lukema perustuu piirille integroituihin DC-DC-muuntimiin, oissa hyötysuhde on 82 prosenttia.

Jatkossa tutkijat aikovat parantaa bondaustekniikkaa, jotta piirien ja välitysalustan (interposer) väliset liitännät saadaan paremmiksi niin sähköisten, mekaanisten kuin lämmönjohto-ominaisuuksien osalta. Pidemmällä aikavälillä CEA-Leti tutkii myös innovatiivista fotonipohjaista johdinkerrostekniikkaa.

Prototyypin 96 laskennallista ydintä on toteutettu kuutena piirinä 28 nanometrin FDSOI-prosessissa. Ne on liitetty alustaan 20 mikrometrin nystyillä. Tutkijoiden mukaan rakenne voidaan skaalata aina 512 ytimeen asti.