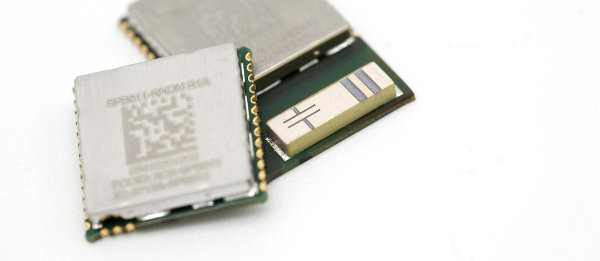

Taiwanilainen TSMC on aasialaisraporttien mukaan tehnyt läpimurron, joka mahdollistaa sirujen valmistamisen peräti 2 nanometrin viivanleveydellä. Tiettävästi kahteen nanometriin siirrytään testimielessä vuonna 2023 ja volyymituotannossa vuotta myöhemmin.

Taiwanilainen TSMC on aasialaisraporttien mukaan tehnyt läpimurron, joka mahdollistaa sirujen valmistamisen peräti 2 nanometrin viivanleveydellä. Tiettävästi kahteen nanometriin siirrytään testimielessä vuonna 2023 ja volyymituotannossa vuotta myöhemmin.

Tällä hetkellä TSMC:n uusin valmistusprosessi on ensimmäisen sukupolven 5 nanometrin prosessi, jota käytetään esimerkiksi Applen tulevien iPhone 12 -puhelimien prosessorien valmistukseen. Kyse on 5 nanometrissä edelleen FinFET-transistoreissa, joissa ”fin” viittaa transistorin evämäiseen rakenteeseen.

FinFETin sijaan TSMC:n 2 nanometrin transistorissa käytetään erilaista rakennetta, jota kutsutaan nimellä MBCFET (Multi-Bridge Channel Field Effect). Kyse on rakenteesta, joka täydentää edellisiä FinFET-malleja.

TSMC:n päätös käyttää MBCFET-mallia transistoreihinsa ei ole uniikki. Jo aiemmin Samsung ilmoitti 3 nanometrin prosessinsa perustuvan samanlaiseen MBCFET-rakenteeseen. Se puolestaan on Samsungin yhdessä IBM:n kehittämän GAAFET-transistorin evoluutio.

Samsungin MBCFET, toisin kuin GAAFET, käyttää nanokalvoa lähteenä ja nieluna, kun GAAFET-rakenteessa käytettiin nanojohtoja. Tämä muutos lisää johtamiseen käytettävissä olevaa pinta-alaa. Lisäksi sen avulla suunnittelija voi lisätä lisää portteja transistoriin lisäämättä sivupintaa.

Viiden nanometrin GAAFET-transistoreja Samsung ja IBM sanoivat pystyvänsä ahtamaan 30 miljardia kappaletta 50 neliömillimetrin tilaan. Tämä tarkoittaa joka tapauksessa, että 2 nanometrin prosessissa transistoritiheys tulee olemaan ennen näkemätön.

Kuva: TSMC