Yksi suurimmista ongelmista laskennassa on nykyään muistikuilu eli ero prosessointiajan ja sen ajan välillä, joka kuluu datan siirtämiseen prosessorille erillisiltä DRAM-muistisiruilta. Amerikkalaistutkijat uskovat, että uudenlainen DRAM-muisti olisi avain ongelmiin.

Yksi suurimmista ongelmista laskennassa on nykyään muistikuilu eli ero prosessointiajan ja sen ajan välillä, joka kuluu datan siirtämiseen prosessorille erillisiltä DRAM-muistisiruilta. Amerikkalaistutkijat uskovat, että uudenlainen DRAM-muisti olisi avain ongelmiin.

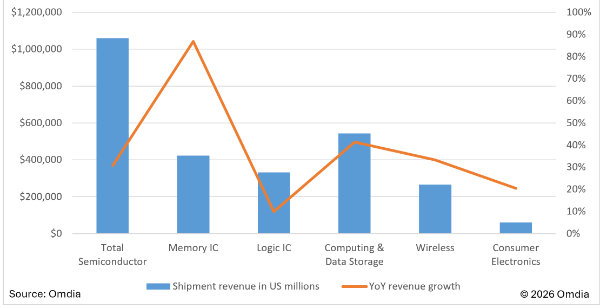

Joulukuussa IEEE:n IEDM-konferenssissa tutkimusryhmät Yhdysvalloissa ja Belgiassa esittelivät yhdessä oksidipuolijohteista valmistettua DRAM-muistia, joka on rakennettu suoraan prosessorin yläpuolelle samalle sirulle. Muisti pystyy varastoimaan bittejä satoja tai tuhansia kertoja kauemmin kuin kaupallinen DRAM, ja se voi tarjota valtavia säästöjä esimerkiksi suurten neuroverkkojen prosessoinnissa.

Tietokoneen DRAM-muistin solut on valmistettu yhdestä transistorista ja yhdestä kondensaattorista, ns. 1T1C-rakenteesta. Jos tähän soluun halutaan kirjoittaa, transistori kytketään päälle ja lataus työnnetään (1) tai poistetaan (0) kondensaattorista. Jos bitti halutaan lukea, pitää varaus mitata.

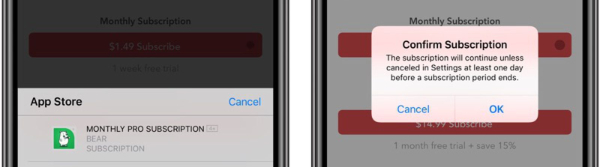

Järjestelmä on erittäin nopea, halpa ja kuluttaa vähän virtaa, mutta sillä on joitain haittoja. Ensinnäkin bitin lukeminen vie virran kondensaattorista, joten lukeminen edellyttää bitin kirjoittamista takaisin muistiin. Lisäksi vaikka bittiä ei luettaisi, varaus vuotaa lopulta kondensaattorista transistorin kautta. Tämän takia kaikki solut on virkistettävä säännöllisesti vain tietojen säilyttämiseksi. Nykyaikaisissa DRAM-siruissa se tehdään 64 millisekunnin välein.

DRAM-muisti on jo upotettu prosessorisiruun myös kaupallisissa piireissä, mutta sillä on rajoituksensa. - Monoliittisen 1T1C-suunnittelun haasteena on aina ollut vaikeus rakentaa kondensaattori sekä valmistaa transistori, jonka vuotovirta olisi erittäin alhainen, sanoo Arijit Raychowdhury, Georgia Techin tietotekniikan professori. Hän työskenteli Notre Damen yliopiston ja Rochesterin teknillisen instituutin tutkijoiden kanssa uuden sulautetun DRAM-muistin parissa. Lyhyesti sanottuna hyviä kondensaattoreita on vaikea tehdä logiikkapiirejä varten rakennetuissa valmistusprosesseissa.

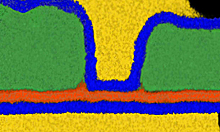

Uusi sulautettu DRAM on sen sijaan valmistettu vain kahdesta transistorista, ilman kondensaattoria (2T0C). Tämä toimii, koska transistorin portti on luonnollinen, vaikkakin pieni kondensaattori. Näin bittiä edustava varaus voidaan tallentaa sinne. Tällä suunnittelulla on joitain keskeisiä etuja, erityisesti tekoälylaskennan kannalta.

Yksi on se, että data voidaan lukea 2T0C DRAM-solusta tuhoamatta tietoja ja joutumatta kirjoittamaan niitä uudelleen. Pitää tarvitsee vain nähdä, virtaako virta transistorin läpi, jonka portti pitää varausta. Jos varaus on olemassa, se kytkee transistorin päälle.

Helppo lukeminen on erityisen tärkeää tekoälylle, koska neuroverkot yleensä lukevat vähintään kolme kertaa jokaisesta kirjoituksesta, kertoo Notre Damen jatko-opiskelija Jorge Gomez.

2T0C-rakenne ei kuitenkaan toimi hyvin piipohjaisten logiikkatransistoreiden kanssa. Transistorin portin kapasitanssi on liian pieni ja vuoto transistoreiden läpi on liian korkea, joten mikä tahansa bitti valuisi heti pois. Tämän ratkaisemiseksi tutkijat ovat siirtymässä amorfisiin oksidipuolijohteisiin, joita käytetään esimerkiksi pikselien ohjaamiseen joissakin näytöissä.

Näillä on useita hienoja ominaisuuksia. Erityisesti niissä voidaan ajaa paljon virtaa, mikä tekee kirjoittamisesta nopeampaa. Ne myös vuotavat hyvin vähän, joten bitti pysyy muistissa paljon kauemmin. Tutkijaryhmä käytti tähän indiumoksidia, johon oli seostettu noin prosentin verran volframia. Yhdistettä he kutsuivat lyhyesti nimellä IWO.

Tämä antaa riittävän luku/kirjoitusnopeuden logiikkaoperaatioita varten. Samanaikaisesti virrat ovat todella pieniä, jopa 2–3 kertaluokkaa pienempiä kuin piillä. Tuloksena voi lopulta olla kaupallinen prosessoripiirille sulautettu DRAM, joka on nopeampi, tiheämpi ja vähemmän tehoa kuluttava kuin mikään nykyinen DRAM-muisti.