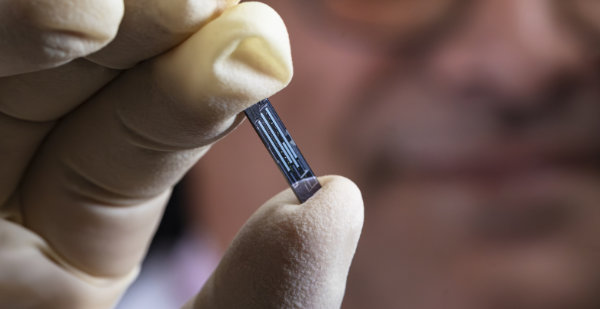

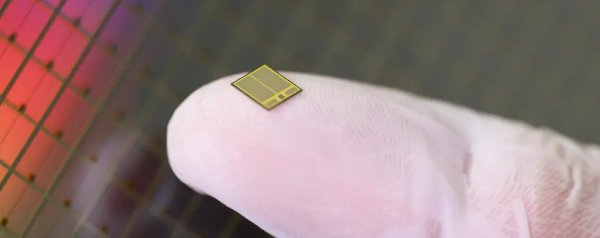

Avoimen RISC-V-arkkitehtuurin kehitys jatkuu ripeänä. Ekosysteemi kasvaa koko ajan ja nyt SiFive ilmoittaa, että sen kehittämä järjestelmäpiiri on onnistuneesti valmistettu TSMC:n 5 nanometrin prosessissa. Asialla on SiFiven OpenFive-divisioona.

Avoimen RISC-V-arkkitehtuurin kehitys jatkuu ripeänä. Ekosysteemi kasvaa koko ajan ja nyt SiFive ilmoittaa, että sen kehittämä järjestelmäpiiri on onnistuneesti valmistettu TSMC:n 5 nanometrin prosessissa. Asialla on SiFiven OpenFive-divisioona.

Järjestelmäpiiriä voidaan käyttää tekoäly- ja HPC-sovelluksiin. SoC:n elementit voidaan myös lisensoida ja käyttää muihin N5-prosessissa valmistettaviin suunnitteluihin malleihin ilman merkittäviä ponnisteluja, SiFive kehuu.

Piiri sisältää 32-bittisen SiFive E76 -suorittimen ytimen AI:lle, mikro-ohjaimille, reunalaskennalle ja muille suhteellisen yksinkertaistetuille sovelluksille. Se käyttää OpenFiven D2D (die-to-die) -liitäntää sekä HBM3-väylän (High Bandwidth Memory) IP -alijärjestelmää, joka sisältää ohjaimen ja jopa 7,2 gigabitin nopeuksia tukevan fyysisen kerroksen.

Uutinen on ilman muuta tärkeä virstanpylväs SiFivelle ja OpenFivelle, koska kyse on ensimmäisestä RISC-V-pohjaisesta piiristä, joka on viety piille 5 nanometrin viivanleveydellä. Myös HBM3-väylä ja lohkojen välinen D2D-liitäntä ovat merkittäviä. D2D käyttää 16 Gbps:n NRZ-signaaleja, IO-linjoja on 40 kanavaa kohti ja parhaimmillaan liitäntä tarjoaa noin 1,75 terabitin kaistan yhdellä millimetrillä.

SoC-suunnittelua voidaan käyttää perustana tulevilla 5 nanometrin SoC-piireille. Ennen kaikkea se on osoitus RISC-V-arkkitehtuurin kyvystä skaalautua kovimpienkin vaatimusten mukaan.