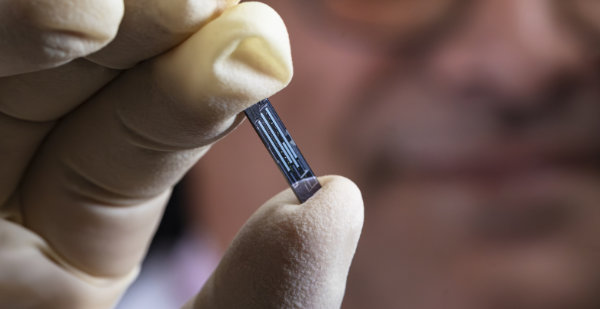

Takavuosina ohjelmoitavaa logiikkaa valmistavat yritykset tulivat valmistustekniikoissa aina 1-2 sukupolvea kehityksen kärkeä perässä. Nyt fpga-valmistaja Xilinx on ensimmäisenä puolijohdeyrityksenä saanut piille 20 nanometrin prosessissa valmistetun piirin. Valmistuskumppanina on tuttuun tapaan taiwanilainen TSMC.

Kisa fpga-valmistajien kesken on kova. Vain kuukausi sitten Altera kertoi tuovansa ensimmäiset 14 nanometrin näytepiirit Intelin FINFET-prosessissa tarjolle jo ensi vuoden alkupuolella. Xilinx nokittaa kilpailijaansa tuomalla 20 nanometrin sirut esiin jo kuluvan vuoden aikana.

20 nanometriä on vaativa viivanleveys. Ensimmäistä kertaa johdinkuviot pitää valmistaa kaksinkertaisella litografilla eli kertavalotus ei tässä kokoluokassa enää onnistu. Tämä nostaa sekä valmistus- että suunnittelukustannuksia, joista Xilinx ei ole kertonut lisätietoja.

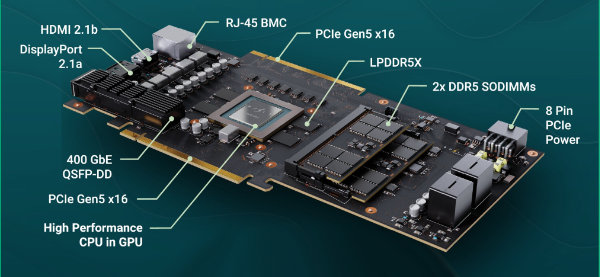

Uuteen viivanleveyteen Xilinx tuo kuitenkin uuden arkkitehtuurin sekä uusitun työkalupaketin. Arkkitehtuurin nimeksi on annettu Ultrascale. Siinä hyödynnetään uusia reititystekniikoita sekä asic-piireistä tuttuja ajastusmenetelmiä. Xilinx kutsuukin Ultrascalea ensimmäiseksi "asic-tasoiseksi" ohjelmoitavaksi logiikaksi.

Uusille työkaluille Xilinx on antanut nimeksi Vivado Design Suite.

Uusien arkkitehtuurien ja valmistustekniikoiden tavoitteena on tietysti lisätä sirujen suorituskykyä ja esimerkiksi tukiasemissa tarvittavien nopeiden liitäntöjen määrää ilman, että kustannukset nousevat kohtuuttomasti. Xilinx lupaakin, että esimerkiksi gigabittitason liitäntöjen määrä suurimmilla piireillä tulee kaksinkertaistumaan.

Xilinx ainakin luottaa uusiin aseisiinsa. Yrityksen mukaan tulevat piirit ovat ainakin vuoden edellä kilpailijoita hintaa, suorituskykyä ja tehonkulutusta verrattaessa. Ensimmäiset Ultrascale-piirit saadaan näytteiksi jo vuoden lopulla.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.