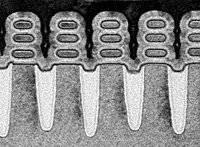

Kymmenessä nanometrissä puolijohdetalot valmistavat siruja FinFET-rakenteina, mutta viidessä nanometrissä niiden rajat tulevat vastaan. IBM on kuitenkin jo valmistanut viiden nanometrin piirejä uudella tekniikalla, jossa hyödynnetään nanoarkkeja (nanosheet).

Yhdessä Globalfoundriesin ja Samsungin kanssa IBM:n tutkijat Albanyn tutkimuskeskuksessa valmistivat viiden nanometrin transistoreja, joiden suorituskyky on 40 prosenttia parempi kuin tehokkaampien tämän päivän 10 nanometrin sirujen.

Kääntäen 5 nanometrin prosessissa voidaan valmistaa yhtä tehokkaita piirejä kuin 10 nanometrissä, mutta 75 prosenttia pienemmällä virrankulutuksella. IBM itse uskoo, että uudella tekniikalla voidaan valmistaa 30 miljardin transistorin jättipiirejä.

IBM kutsuu uutta rakennetta nimellä GAAFET (gate-all-around FET). Uudessa rakenteessa transistorit koostetaan nanoarkeilla. Niiden leveyttä voidaan hallita EUV-litografialla, joten IBM:n transistorit ovat myös tämän tulevaisuuden tekniikan ensimmäinen käytännöllinen sovellus. EUV:ssä käytetään 13,5 nanometrin laseria, kun tämän hetken piirienvalmistuksessa valonlähteenä on 193 nanometrin laser.

IBM:n mukaan 5 nanometrin piiritekniikka on tulossa kaupalliseen käyttöön "ei niin kaukaisessa tulevaisuudessa".