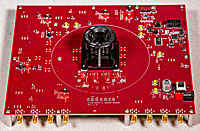

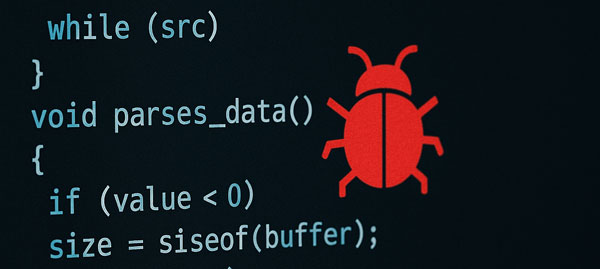

JEDEC työstää DDR-väylän seuraavaa versiota. Esistandardi on jo aika pitkällä, joten Cadence on esitellyt ensimmäisen toimivan DDR5-testipiirin. TSMC:n 7 nanometrin prosessissa valmistettu ohjain siirtää dataa 4400 megasiirtoa sekunnissa.

DDR5:n nopeus on 37,5 prosenttia rivakampi kuin tämän hetken DDR4-väyläisissä muisteissa. Uusi standardi tulee näin merkitsemään selvää hyppäystä eteenpäin datansiirrossa muistin ja prosessorin välillä.

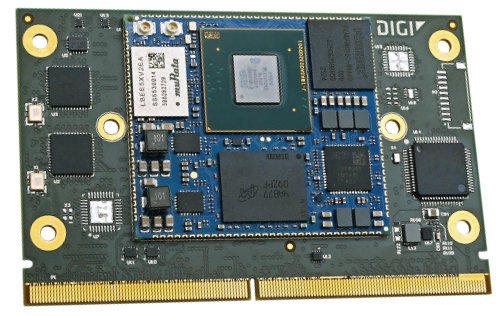

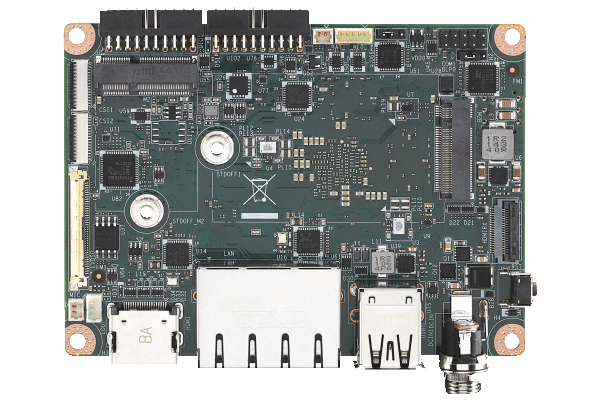

Testipiiri sisältää sekä fyysisen osan että ohjaimen DDR5-väylän toteutukseen. Toimivan piirin toteutus osoittaa, että Cadencen DDR5-IP:llä voidaan pian ryhtyä valmistamaan huippunopeita DDR5-alijärjestelmiä palvelimiin, tallennuslaitteisiin ja muihin yrityssovelluksiin, joihin DDR5-tekniikan uskotaan ensiksi saapuvan.

Osana Cadencen testiohjelmaa DRAM-valmistaja Micron on toimittanut sille ensimmäiset DDR5-standardia tukevat protomuistit.

Cadencen mukaan monet sen järjestelmäpiiriasiakkaat alkavat pian suunnitella DDR5-muistia hyödyntäviä järjestelmiä. JEDEC on luvannut lopullisen standardin valmiina tämän vuoden aikana. Ensimmäisiä DDR5-järjestelmiä voidaan odottaa markkinoille ehkä jo ensi vuonna, viimeistään vuoden 2020 alkupuolella.