Japanilaisen Tohoku-yliopiston tutkijat kertoivat äskettäisessä IEEE:n International Solid State State Circuit -konferenssissa kehittäneensä mikro-ohjaimen, joka on erittäin suorituskykyinen ja kuluttaa erittäin vähän tehoa. Tämäon seurausta spintroniikkaan perustuvan suunnittelun hyödyntämisestä.

Japanilaisen Tohoku-yliopiston tutkijat kertoivat äskettäisessä IEEE:n International Solid State State Circuit -konferenssissa kehittäneensä mikro-ohjaimen, joka on erittäin suorituskykyinen ja kuluttaa erittäin vähän tehoa. Tämäon seurausta spintroniikkaan perustuvan suunnittelun hyödyntämisestä.

Pienen tehonkäytön ja suorituskykyisten mikro-ohjaimien kysyntä on kasvanut tehonkäytölle kriittisten IoT-antureiden solmujen sovelluksissa. Tällaisten sovellusten vaatimia mikro-ohjaimia on aktiivisesti tutkittu ja kehitetty, mutta nykyisillä elektroniikkaan perustuvilla ratkaisuilla on omat rajoitteensa, vaikka niissäkin on jo päästy pitkälle tehonkulutuksen kutistamisessa.

Professorien Tetsuo Endohin, Takahiro Hanyun ja Masanori Natsuin tutkimusryhmän kehittämän mikro-ohjaimen tehonkulutus on 200 megahertsin kellotuksella 47,14 mikrowattia.

Tässä spintroniikkaan perustuvassa MCU:ssa kaikki moduulit tehdään haihtumattomiksi spintronisilla piirirakenteilla. Tehonkulutusta hillitään hallitsemalla jokaisen moduulin teholähdettä itsenäisesti. Lisäksi logiikan ja muistin datansiirron pullonkaula vapautuu muistiohjaimella, joka voi nopeuttaa koko järjestelmää. Uudelleen konfiguroitava kiihdytysmoduuli voi ajaa sovelluskohtaista signaalinkäsittelyä.

Tämä MCU-piiri tarjoaa professorien mukaan sekä maailman korkeimman suorituskyvyn että energiatehokkuuden IoT-anturisolmuille, joita käytetään kerätyllä energialla. Keruuenergia on peräisin ulkoisista lähteistä, kuten aurinkoenergiasta tai lämpöenergiasta.

Tutkijoiden testeissään saavuttama tehonkäyttö 200 megahertsin kellotaajuudella oli 47,14 mikrowattia. Megahertsiä kohti tämä tarkoittaa 0,235 mirowatin kulutusta, kun se esimerkiksi NXP:n pienen tehonkäytön Arm Cortex-M4 -pohjaisella 32-bittisellä ohjaimella on luokkaa 140 μW/MHz.

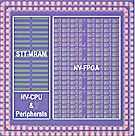

Tohoku yliopiston Tetsuo Endohin johtama spintroniikan tutkimuskeskus (Center for Spintronics Integrated Systems) on paneutunut spintronisiin tekniikoihin ja tutkinut muun muassa valmiustilan tehoa käyttämättömän FPGA:n toteutusta hakutaulukolla, jossa hyödynnetään spin-siirto-momentin magneettista tunneliliitosta (STT-MTJ) ja MOS-transistoreita.

Tutkijoiden mukaan MTJ-piirirakenne on paras ehdokas käytännöllisesti katsoen rajoittamattomalle kestävyyden, CMOS-yhteensopivuuden ja 3D-pinottavuuden kannalta. He ovat toteuttaneet esimerkiksi MTJ-pohjaisen, haihtumattoman LUT-piirin suunnitelman, jossa on datan päivittäminen minimoidulla siirtymävaiheella erittäin vähävirtaiselle FPGA-piirille.

Veijo Hänninen

Nanobittejä 7.3.2019