Uusimmat FPGA-piirit ovat massiivisia järjestelmäpiirejä, joissa FPGA-osan lisäksi on prosessoreja, DSP-lohkoja, grafiikkaprosessoreja, tekoälysuorittimia ja koko joukko muuta toiminnallisuutta. Tällaisen kokonaisuuden ohjelmointi vaatii periaatteessa erittäin laajaa laitesuunnittelun osaamista. Ei enää, väittää FPGA-talo Xilinx.

Uusimmat FPGA-piirit ovat massiivisia järjestelmäpiirejä, joissa FPGA-osan lisäksi on prosessoreja, DSP-lohkoja, grafiikkaprosessoreja, tekoälysuorittimia ja koko joukko muuta toiminnallisuutta. Tällaisen kokonaisuuden ohjelmointi vaatii periaatteessa erittäin laajaa laitesuunnittelun osaamista. Ei enää, väittää FPGA-talo Xilinx.

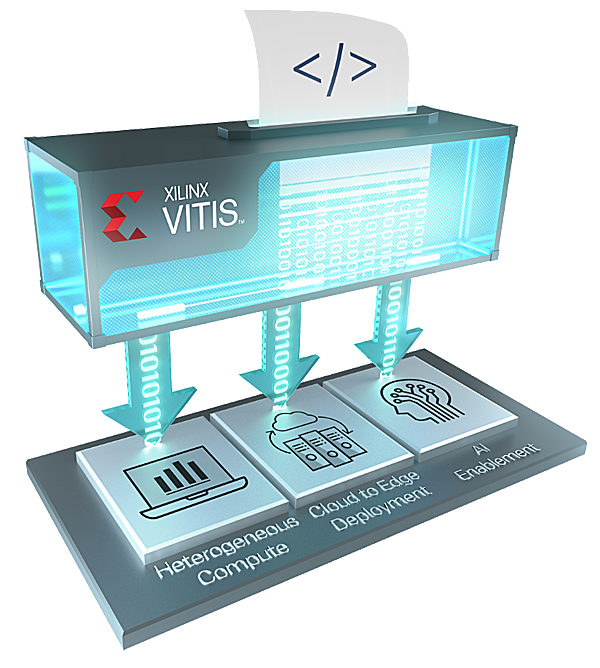

Xilinx on esitellyt uuden Vitis-kehitysalustan, jota talon sisällä on kehitetty viiden vuoden ajan ja tuhannen miestyövuoden verran. Kyse on alustasta, joka räätälöi Xilinx-laitteiston (FPGA-matriiseineen) softa- tai algoritmikoodiksi ilman, että prosessissa vaaditaan HDL-ohjelmoinnin asiantuntemusta.

Vitis ei ole perinteinen yritys- tai laite/arkkitehtuurispefisi kehitysympäristö, vaan se liittyy suoraan yleisiin ohjelmistonkehitystyökaluihin. Vitis-ohjelmoinnissa voidaan hyödyntää laajaa valikoimaa avoimen koodin kirjastoja, joten koodaaja voi keskittyä algoritmeihinsa.

Vitis-alustaa on kehitetty Xilinxin Vivadon pohjalta, mutta kyse on uudesta kehyksestä. Vivado on laajalti Xilinxin FPGA-asiakkaiden käytössä ja sen tukea yhtiö lupaa jatkaa, mikäli nämä haluavat jatkaa VHDL- ja Verilog-koodaamista. Xilinxin mukaan Vitis voi tosin tuoda teholisän myös näille suunnittelijoille, kun laitemoduuleja voidaan kutsua toimintoina suoraan ohjelmistosta.

Xilinxin mukaan Vitis on ohjelmistopinopohjainen arkkitehtuuri, jossa on neljä kerrosta. Pohjalla on Vitis-kohdelaitteisto, johon sisältyy kortti ja esiohjelmoitu I/O-järjestelmä. Toisessa kerroksessa on Vitis-ydinkehityspaketti. Siinä Xilinxin oma avoin ajonaikainen kirjasto hallitsee datan liikuttelua järjestelmän eri osien välillä. Osiin voi kuulua esimerkiksi Xilinxin tulevien Vercal ACAP -järjestelmäpiirien tekoälymoottori.

Kolmannella tasolla alustaan kuuluu yli 400 optimoitua avoimen koodin sovellusta kahdeksassa ei Vitis-kirjastossa. Näihin kuuluu esimerkiksi konenäkökirjasto, lineaarialgebrakirjasto BLAS, tietokantakirjadto, jne. Näiden avulla kehittäjä voi kutsua valmiiksi kiihdytettyjä toimintoja piirille standardin ohjelmointirajapinnan kautta.

Xilinxin mukaan keskeisin kerros ja samalla koko FPGA-markkinan kannalta mullistavin on neljäs eli Vitis AI. Siinä FPGA-piirin resurssit optimoidaan ja ohjelmoidaan hyödyntämään suosituimpien tekoälykehysten (kuten TensorFlow ja Caffe) malleja. Käytännössä koodaajalle annetaan työkalut, joilla voidaan optimoida, pakata ja kääntää valmiita AI-malljea ajettavaksi suoraan FPGA-piirillä. Tämä kaikki onnistuu noin minuutissa, Xilinx kehuu.

Vitis AI:n rinnalle Xilinx lupaa pian tuoda toisen sovellusspesifin arkkitehtuurin, joita se kutsuu nimellä DSA (domainspesific architecture). Tämä Vitis Video mahdollistaa videoenkoodauksen tuomisen FPGA-piirillä yksinkertaisella koodikutsulla. Myös Xilinxin kumppanit kehittävät omia DSA-arkkitehtuureitaan, joita voidaan hyödyntää Vitis-kehityksessä.

Vitis-työkalut tulevat ensi kuussa ladattavaksi Xilinxin korttiasiakkaille.