Viime vuosina yritykset ovat kasvattaneet NAND-piirien tiheyttä ennen kaikkea rakentamalla soluja myös pystysuunnassa. Toshiba ilmoitti puolestaan ensimmäisenä ryhtyvänsä valmistamaan NAND-flasheja PLC-rakenteella (penta level cell). Nyt Intel kertoo ryhtyvänsä samaan.

Viime vuosina yritykset ovat kasvattaneet NAND-piirien tiheyttä ennen kaikkea rakentamalla soluja myös pystysuunnassa. Toshiba ilmoitti puolestaan ensimmäisenä ryhtyvänsä valmistamaan NAND-flasheja PLC-rakenteella (penta level cell). Nyt Intel kertoo ryhtyvänsä samaan.

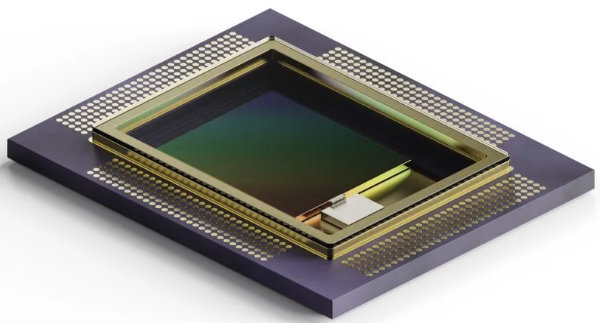

Tällä hetkellä valmistajat ovat päässeet suhteellisen luotettavaan QLC-tallennukseen (quad level cell). Siinä jokaiseen NAND-soluun voidaan tallentaa neljä bittiä. Piilaakson Hot Chips -konferenssissa elokuussa Toshiba kertoi kuitenkin kehittelevänsä jo seuraavan sukupolven BiCS-tekniikkaa, jossa samaan soluun voidaan tallentaa viisi bittiä dataa.

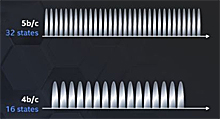

Tämä on kuitenkin iso haaste. Jotta soluun voitaisiin tallentaa viisi bittiä, pitää siinä pystyä erottelemaan peräti 32 eri jännitetasoa. Tämä on luotettavasti erittäin vaikeaa. Lisäksi ohjaimen pitää pystyä lukemaan nämä eri nanoluokan jännite-erot luotettavasti, muutenhan sirussa ei ole järkeä.

Yksinkertaisin NAND-piiri on SLC-tyyppiä (single level cell). Siinä kelluvaan hilaan perustuva rakenne on joko latautunut tai ei ole, mikä kuvaa bitin ykköstä tai nollaa. Tätä rakennetta voidaan kirjoittaa erittäin nopeasti ja se myös kestää eniten kirjoitusjaksoja.

SLC-piirit ovat kuitenkin kalliita valmistaa, koska kapasiteetti vie eniten piialaa. Sen takia soluihin on lisätty jännitetasoja, uusimmissa PLC-piireissä jo 32 eri tasoa. Vaikka kapasiteetti kasvaa selvästi, jännite-erojen tunnistaminen tekee lukemisesta ja kirjoittamisesta hitaampaa. Kuluttajalaitteissa tällä ei ole niin suurta merkitystä.