Autoelektroniikan järjestelmien säännöllisen, avoimen testauksen tarve tulee jatkuvasti kasvamaan, kun turvallisuuden kannalta kriittisten toimintojen määrä ja kompleksisuus lisääntyvät, kertoo Siemens-konserniin kuuluva Mentor ETNdigi-lehden artikkelissa.

Autoelektroniikan järjestelmien säännöllisen, avoimen testauksen tarve tulee jatkuvasti kasvamaan, kun turvallisuuden kannalta kriittisten toimintojen määrä ja kompleksisuus lisääntyvät, kertoo Siemens-konserniin kuuluva Mentor ETNdigi-lehden artikkelissa.

Ennen kuin itseohjautuvat ajoneuvot ovat todellisuutta, autoelektroniikan puolijohdeosien suunnittelussa ja testaamisessa on tehtävä perustavaa laatua olevia muutoksia.

Autoelektroniikan piirien kehityksessä ja valmistamisessa käytetään yhä enenevässä määrin uusimpia huipputekniikan prosesseja. Piireillä ei enää toteuteta pelkästään yksinkertaisia toimintoja, kuten ikkunoiden tai valojen ohjausta, vaan niiden on kyettävä suorittamaan yhä moni- puolisempia toimintoja, jotka liittyvät ajajaa avustaviin järjestelmiin (ADAS) ja yhä enemmän erityisesti itseohjautuvan ajamisen sovelluksiin.

Vaadittavien toimintojen monipuolistuminen edellyttää autoelektroniikan piireiltä entistä parempaa suorituskykyä, jolloin on tarve saada suuret ja monimutkaiset IC-piirit toteutetuksi siten, että ne ovat teho-ominaisuuksiltaan mahdollisimman optimaaliset. Piirien tulee täyttää myös tiukimmat mahdolliset ISO 26262:n mukaiset turvallisuusmääräykset, mikä yhdessä edellä mainittujen optimaalisten teho-ominaisuus- vaatimusten kanssa asettaa aivan uudenlaisia haasteita autoelektroniikan piirien ja järjestelmien valmistajille. Ratkaisuja tarvitaan, jotta pystytään takaamaan uusien edistyneiden autoelektroniikan järjestelmien turvallinen toiminta kaikissa mahdollisissa tilanteissa koko ajoneuvon elinkaaren ajan. Tätä tarkoitetaan toiminnallisen turvallisuuden tavoittelulla.

Toiminnallinen turvallisuus nojaa suunnitteluun kuuluviin mekanismeihin, niin kutsuttuihin turvallisuus- mekanismeihin, joiden avulla voidaan valvoa ja tarkistaa, että suunnittelun sisältämä toiminnallisuus on virheetöntä toiminnan aikana. Nämä turvallisuusmekanismit paljastavat sekä piilevät että hetkelliset mahdolliset virhetilanteet, jolloin saadaan määritettyä suunnittelun kokonaisvaltaisesti kattava diagnostiikka, mikä puolestaan määrittää suunnittelun saavuttaman ASIL-luokituksen (Automotive Safety Integrity Level) mukaisen turvallisuustason.

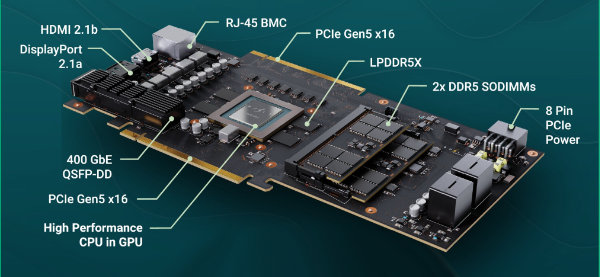

Erittäin suosittu lähestymistapa on hajauttaa sulautettuja toimintoja eri puolille puolijohdepiirejä ja yhdistää hajautetut toiminnot keskenään yhteisellä tiedonsiirtoväylällä, jonka ansiosta eri puolilla järjestelmää tapahtuvat satunnaiset virhetilanteet on mahdollista nopeasti tunnistaa ja raportoida eteenpäin. Sulautetut valvontatoiminnot eivät saa aiheuttaa häiriöitä normaalien toimintojen suorittamisessa ja niiden on joustavasti pystyttävä antamaan tietoa eritasoisista virhetilanteista, jotka perustuvat puolijohdepiirin loppusovellukseen ja siihen liittyviin ASIL-luokituksiin. Ylläolevassa kuvassa on esitetty esimerkki hajautettua järjestelmätason valvontaa tukevasta piiritason testausarkkitehtuurista.

Standardin IEEE 1149.1 mukainen testiliitäntäpiste (TAP) toimii porttina kaikkiin piirin sisäisiin testausresursseihin valmistuksen aikaista testaus- ta varten. TAP liitetään standardiin IEEE 1687 (usein kutsutaan IJTAG-standardiksi) perustuvaan rekonfiguroitavaan sarjapääsyverkkoon. Tämä IJTAG-verkko koostuu kytkimistä, joita kutsutaan lohkoliitäntäbiteiksi (SIB). Jokainen SIB sallii alaverkon kytkemisen tai ohittamisen, jolloin voidaan optimoida pääsy mihin tahansa testausresurssiin verkossa. Pääsy IJTAG-verkkoon on myös järjestelmän sisäisestä testauksesta (IST) huolehtivalla ohjaimella. IST-ohjain välittää tietoa CPU-rajapinnan läpi joko ulkomaailmaan tai sisäiseen turvallisuushallintayksikköön ja suorittaa tarpeelliset datan rinnakkais-sarja- ja sarja- rinnakkaismuunnokset tiedon siirtämiseksi CPU-väylän ja sisäisen IJTAG-verkon välillä. Tämä IST- ohjaimella voidaan toteuttaa kuvassa 2 esitetyn kaltainen järjestelmätason tiedonsiirtoarkkitehtuuri.

Palvelimen prosessorilla on pääsy kuhunkin IST-ohjaimeen ja siten mihin tahansa piirin sisäiseen testausresurssiin millä tahansa ajoneuvoväylän, kuten CAN- tai I2C- väylän, runkoratkaisulla.

Käytettäessä kehittyneitä SOC- piirejä turvallisuushallintayksikkö voidaan vaihtoehtoisesti sulauttaa osaksi piiriä. Tällaista arkkitehtuuria nimitetään yleisesti turvallisuus- saarekkeeksi. Termiä saareke käytetään, koska halutaan tuoda esiin, että turvallisuushallintayksikkö altistuu mahdollisimman vähän piirin toiminnasta aiheutuville häiriöille. Tämä taataan siten, että turvallisuus- hallintoyksikkö on toteutettu fyysisesti ja tehonsyötön osalta erillisenä osiona puolijohteelle, jolloin se vastaanottaa erityiset teho- ja ohjaussignaalit, ja on eristetty fyysisesti toimintalogiikasta niin hyvin kuin mahdollista. Ainoana datayhteytenä ovat liitännät testausverkkoon.

Onko järjestelmän hajauttaminen tehokkaampaa yksittäiselle vai useammalle piirille riippuu siitä, minkälaisia testausresursseja erilaiset piirit käsittävät. ISO 26262 - sertifiointi edellyttää, että mainitut resurssit käsittävät tyypillisimmin valikoiman erilaisia toiminnallisia ja rakenteellisia turvallisuusmekanismeja. Todennäköisesti yleisimmin tunnettu piirin sisäisen rakenteellisen resurssin muoto on sisäänrakennettu muistin itsetestaus (MBIST). MBIST- ydin testaa sulautetun muistin muodostamalla algoritmeihin perustuen luku- ja kirjoitus- toimintojen sekvenssejä, jotka kattavat koko osoiteavaruuden.

Suurin haaste tällaisen muistitestauksen suorittamisessa ajoneuvon käynnissä ollessa on, että muisti pitää ensin kytkeä irti järjestelmästä, jotta BIST-ydin pystyy ottamaan ohjat käsiinsä. Saattaa olla myös tarpeen varmuuskopioida muistin sisältö ennen testauksen suorittamista ja palauttaa sisältö jälkikäteen, koska muistitestauksen aikana saattaa tuhoutua testausta ennen ollutta muistisisältöä. Toinen ongelmakohta on muistin kytkeminen irti järjestelmästä, jolloin järjestelmän suorituskyky todennäköisesti heikkenee. Joidenkin sovellusten yhteydessä ei ole hyväksyttävää.

Edellä mainittujen ongelmien välttämiseksi on kehitetty muisti- sisältöön kajoamaton MBIST- teknologia. Tässä lähestymistavassa MBIST-ydin testaa muistia käyttäen transaktioiden lyhytsekvensseistä koostuvia sarjoja, joita yleensä kutsutaan purskeiksi. Purskeen kesto on tyypillisesti tietty kohtuullinen määrä kellojaksoja (ehkä 20 tai 30) ja sen kohteena on joka kerta eri muistipaikat. Koko muisti saadaan näin ollen testatuksi suurella määrällä lyhyitä MBIST- jaksoja. Lähestymistapa on kajoamaton, koska jokaisen purskeen aikana MBIST-ydin tallentaa ja palauttaa purskeen modifioitavana olevat muistipaikat. Toiminnallinen suorituskyky ei merkittävästi heikkene, koska aivan purskeiden alkuvaiheessa MBIST- ytimen ja toimintalogiikan välinen satunnaislogiikka määrittelee, että muisti on vapaa.

Looginen BIST on toinen suosittu muoto toteuttaa rakenteellisesti järjestelmän sisäinen testausresurssi, johon päästään käsiksi IST- ohjaimella. Tässä testausratkaisussa piirissä synnytetään satunnaiskuvioita, joissa muodostetaan skannausketjuja piirin logiikkaosan testausta varten. Piirin antamat vasteet kaikkiin satunnaiskuvioihin

kootaan allekirjoitukseksi, joka tutkinnan tuloksena testin lopuksi joko hyväksytään tai hylätään. Testin kattavuus lisääntyy eksponentiaalisesti, mitä suurempi määrä satunnaiskuvioita on käytettävissä.

Haasteena tässä lähestymistavassa on saavuttaa riittävän suuri kattavuus testeille järkevissä kustannus- raameissa. Ratkaisuna tähän on viipaloida testaus useisiin aika- jaksoihin. Peräkkäiset viipaloidut testausjaksot testaavat tietyn ajanjakson ajan piirin toimintaa. Esimerkiksi kuvadataa käsittelevässä kuvaprosessorissa jokainen testijakso voidaan asettaa tapahtumaan, kun yksittäisen kuvakehyksen käsittely vaihtuu toiseen. Useiden testausjaksojen hallinta vaatii huolellisesta koordinaatiota IST-ohjaimen ja loogisen BIST-ytimen välillä. IST- ohjaimen on tarkasti tiedettävä seuraavaksi suoritettava testaus- jakso, alustettava looginen BIST-ydin oikeanlaisen satunnaiskuvioiden joukon luomiseksi ja sen jälkeen etsittävä ja tutkittava asianomainen allekirjoitus ja sen perusteella tehtävä päätös hyväksynnästä tai hylkäämisestä.

On tapauksia, jolloin kuvatun mallinen hajauttaminen ei ole mahdollista tai sillä ei saavuteta riittävää kattavuutta vikasietoisella aikajaksolla (FTTI). Käytettävissä on uusi teknologia, jolla saadaan merkittävästi lyhennettyä loogisten BIST-valvontajaksojen vaatimaa testausaikaa, mikä puolestaan parantaa merkittävästi kokonaisvasteaikaa.

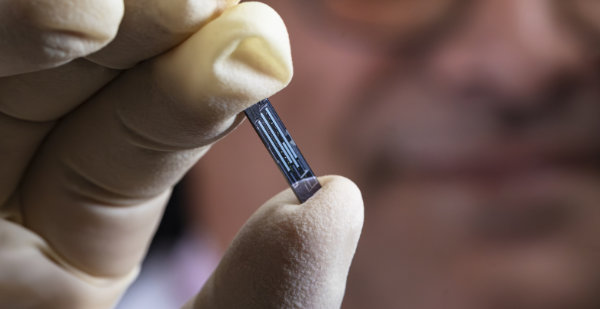

Uuden OST-testausteknologian (Observation Scan Technology) ansiosta looginen BIST hyödyntää erityisiä piirisuunnitteluun upotettuja testauspisteitä osana OST-testaus- alkioista koostuvaa pientä erityistä testausketjua, jossa testausalkiot tehokkaasti keräävät vikatietoa toimintalogiikasta jokaisella siirtojaksolla, sen sijaan että vikatietoa kerättäisiin vain jokaisella kuviojaksolla. Tätä kuvataan ylläolevassa kuvassa.

Tuloksena on merkittävästi nopeammin saavutettava toiminta- logiikan kattava testaus, jolloin turvallisuusmekanismin edellyttämät laatuvaatimukset saavutetaan paljon nopeammin kuin perinteisiä loogisia BIST-piirejä käytettäessä.

Kaikkia yllä kuvattuja teknologioita ja metodologioita hyödyntämällä voidaan rajattomasti lisätä järjestelmätason turvallisuuteen liittyviä toimintoja. Testaus voidaan aloittaa ja lopettaa helposti antamalla käskyt kaikille IST-ohjaimille, jotta niiden kaikki testausresurssit ovat käytettävissä valitun skenaarion mukaisten testausten suorittamista varten.

Kaikki testausvirheet raportoidaan takaisin turvallisuudenhallinta- yksikköön, joka voi vastaanottamiensa tulosten perusteella käskyttää eritasoisia korjaavia toimia alkaen yksinkertaisista näytölle ilmaantuvista varoitusilmoituksista päätyen ajoneuvon pysäyttämiseen huoltotoimenpiteitä varten.

IST-ohjaimet voidaan myös määrätä suorittamaan säännöllisesti toistuvia testijaksoja turvallisuuden kannalta kriittisistä toiminnoista vastaavissa osissa elektroniikkajärjestelmää aina silloin kun ajoneuvo on käytössä. Turvallisuushallintayksikkö jälleen tutkii testeistä saatavat virhetulokset ja antaa asianmukaista vastetta, kuten yksinkertaisimmillaan ajaa alas tiettyjä ADAS-toimintoja tai jämerämpänä toimena asettaa ajoneuvon johonkin turvalliseen toimintatilaan. Näin käy silloin, jos edellä mainittujen turvallisuus- mekanismien vasteaika muodostuu kriittiseksi.

Autoelektroniikan järjestelmien säännöllisen, avoimen testauksen tarve tulee jatkuvasti kasvamaan, kun turvallisuuden kannalta kriittisten toimintojen määrä ja kompleksisuus lisääntyvät kaiken aikaa. Joitakin kaupallisia ratkaisuja tähän tarpeeseen on jo esitelty ja lisää on tulossa.

Lue tämä ja muut artikkelit uudesta ETNdigi-lehdestä.

https://issuu.com/etndigi/docs/etndigi1_2020?fr=sYTQ1YTE0NTQ5NDc

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.