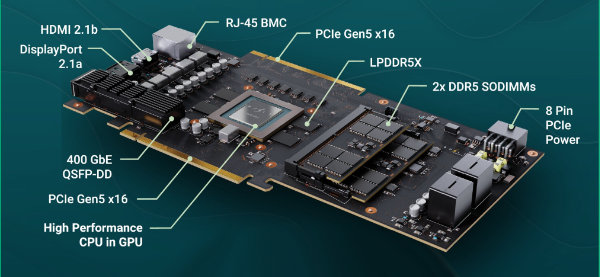

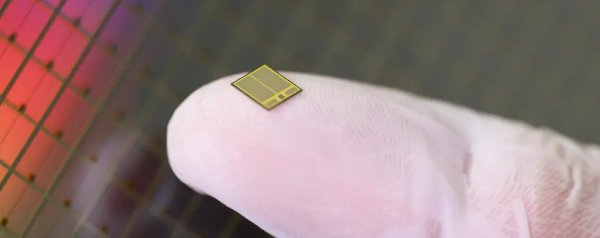

Ruotsalaistutkijat Linköpingin yliopistossa ovat kehittäneet yksinkertaisen menetelmän, jolla monissa sovelluksissa käytettyjen standardialgoritmien laskenta voi tehostua jopa viisinkertaiseksi. Metodi perustuu FPGA-piirin käyttämiseen laskennassa.

Linköpingiläistutkijat ovat tehostaneet FPGA-piirin avulla hyvin tavanomaisen algoritmin laskentaa eli FFT-muunnosta (Fast Fourier Transform). Sitä käytetään esimerkiksi spektrianalysiissä sekä tutka- ja tietoliikennesovelluksissa.

Useita vuosia sitten silloinen opiskelija Carl Ingemarsson sai opettajaltaan haasteen saada FFT-muunnos toimimaan FPGA-piirillä nopeammin kuin 450 megahertsin kellotaajuudella. Palkintona oli lukuvuoden viimeisestä tehtävästä vapautuminen.

Ingemarsson ryhtyi tutkimaan, miltä logiikka itse asiassa näytti piirin sisällä. Innostus muuttui lopulta väitöskirjatyöksi sekä innovaatioksi, jonka perusteella nykyiset FPGA-piirit voivat laskea viisi kertaa nopeammin tai tehdä viisi kertaa enemmän prosesseja. Tekniikkaa on testattu kahdella FPGA-piiriperheellä, mutta ei ole mitään esteitä sille, etteikö metodi toimisi kaikilla FPGA-piireillä.

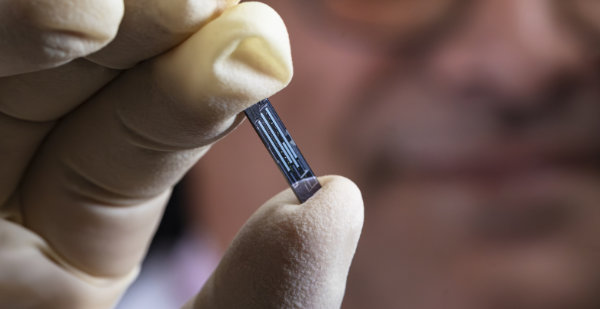

Ingemarsson on tutkinut sitä, miten signaali voisi kulkea älykkäämmin piirin matriisin sisällä. Normaalisti valitaan algoritmi ja rakennetaan sen ympärille rakenne tai arkkitehtuuri niiden lohkojen kera, joita laskennassa tarvitaan. Tämä suunnitelma viedään sitten FPGA-piirille.

Ingemarsson on sen sijaan mapannut tai reitittänyt signaalit piirin sisällä uudella tavalla. Arkkitehtuuri on tavallaan sovitettu algoritmiin. Muuttamalla signaalipolkuja älykkäämmiksi on päästy jopa viisinkertaiseen parannukseen laskentatehossa.

Ulkoa päin piirit näyttävät edelleen samoilta vakiokomponenteilta. Tämän takia myös löydöksen julkaiseminen tieteellisessä aikakauslehdessä oli pitkään hankalaa. - Päältä päin näyttää siltä, että emme ole tehneet yhtään mitään, Ingemarsson selittää.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.